APPENDIX

# Assemblers, Linkers, and the SPIM Simulator

James R. Larus Microsoft Research Microsoft

Fear of serious injury cannot alone justify suppression of free speech and assembly.

**Louis Brandeis**

Whitney v. California, 1927

**A.1** Introduction A-3 **A.2 Assemblers** A-10 **A.3** Linkers A-18 **A.4** Loading A-19 **A.5** Memory Usage A-20 **A.6 Procedure Call Convention** A-22 **A.7 Exceptions and Interrupts** A-33 **A.8** Input and Output A-38 **A.9** SPIM A-40 A.10 MIPS R2000 Assembly Language A-45 **A.11 Concluding Remarks** A-81 A.12 Exercises A-82

# **A.1**

### Introduction

Encoding instructions as binary numbers is natural and efficient for computers. Humans, however, have a great deal of difficulty understanding and manipulating these numbers. People read and write symbols (words) much better than long sequences of digits. Chapter 2 showed that we need not choose between numbers and words because computer instructions can be represented in many ways. Humans can write and read symbols, and computers can execute the equivalent binary numbers. This appendix describes the process by which a human-readable program is translated into a form that a computer can execute, provides a few hints about writing assembly programs, and explains how to run these programs on SPIM, a simulator that executes MIPS programs. UNIX, Windows, and Mac OS X versions of the SPIM simulator are available on the CD.

Assembly language is the symbolic representation of a computer's binary encoding—machine language. Assembly language is more readable than machine language because it uses symbols instead of bits. The symbols in assembly language name commonly occurring bit patterns, such as opcodes and register specifiers, so people can read and remember them. In addition, assembly language

machine language Binary representation used for communication within a computer system.

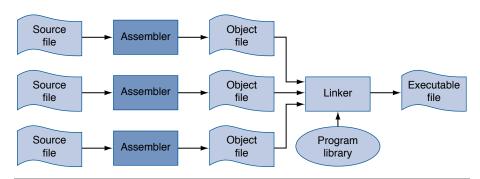

**FIGURE A.1.1** The process that produces an executable file. An assembler translates a file of assembly language into an object file, which is linked with other files and libraries into an executable file.

permits programmers to use *labels* to identify and name particular memory words that hold instructions or data.

A tool called an **assembler** translates assembly language into binary instructions. Assemblers provide a friendlier representation than a computer's 0s and 1s that simplifies writing and reading programs. Symbolic names for operations and locations are one facet of this representation. Another facet is programming facilities that increase a program's clarity. For example, **macros**, discussed in Section A.2, enable a programmer to extend the assembly language by defining new operations.

An assembler reads a single assembly language *source file* and produces an *object file* containing machine instructions and bookkeeping information that helps combine several object files into a program. Figure A.1.1 illustrates how a program is built. Most programs consist of several files—also called *modules*—that are written, compiled, and assembled independently. A program may also use prewritten routines supplied in a *program library*. A module typically contains *references* to subroutines and data defined in other modules and in libraries. The code in a module cannot be executed when it contains *unresolved references* to labels in other object files or libraries. Another tool, called a *linker*, combines a collection of object and library files into an *executable file*, which a computer can run.

To see the advantage of assembly language, consider the following sequence of figures, all of which contain a short subroutine that computes and prints the sum of the squares of integers from 0 to 100. Figure A.1.2 shows the machine language that a MIPS computer executes. With considerable effort, you could use the opcode and instruction format tables in Chapter 2 to translate the instructions into a symbolic program similar to Figure A.1.3. This form of the

**assembler** A program that translates a symbolic version of an instruction into the binary version.

macro A pattern-matching and replacement facility that provides a simple mechanism to name a frequently used sequence of instructions.

unresolved reference A reference that requires more information from an outside source in order to be complete.

**linker** Also called link editor. A systems program that combines independently assembled machine language programs and resolves all undefined labels into an executable file.

A.1 Introduction A-5

```

0010011110111101111111111111100000

10101111101111111000000000000010100

101011111010010000000000000100000

101011111010010100000000000100100

1010111110100000000000000000011000

1010111110100000000000000000011100

1000111110101111000000000000011100

100011111011100000000000000011000

000000011100111000000000000011001

0010010111001000000000000000000000

00101001000000010000000001100101

1010111110101000000000000000011100

000000000000000000111100000010010

101011111011100100000000000011000

00100100100001000000010000110000

1000111110111111100000000000010100

0000000000000000000100000100001

```

FIGURE A.1.2 MIPS machine language code for a routine to compute and print the sum of the squares of integers between 0 and 100.

routine is much easier to read because operations and operands are written with symbols, rather than with bit patterns. However, this assembly language is still difficult to follow because memory locations are named by their address, rather than by a symbolic label.

Figure A.1.4 shows assembly language that labels memory addresses with mnemonic names. Most programmers prefer to read and write this form. Names that begin with a period, for example .data and .globl, are assembler directives that tell the assembler how to translate a program but do not produce machine instructions. Names followed by a colon, such as str or main, are labels that name the next memory location. This program is as readable as most assembly language programs (except for a glaring lack of comments), but it is still difficult to follow because many simple operations are required to accomplish simple tasks and because assembly language's lack of control flow constructs provides few hints about the program's operation.

By contrast, the C routine in Figure A.1.5 is both shorter and clearer since variables have mnemonic names and the loop is explicit rather than constructed with branches. In fact, the C routine is the only one that we wrote. The other forms of the program were produced by a C compiler and assembler.

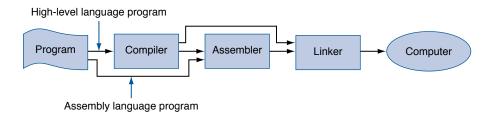

In general, assembly language plays two roles (see Figure A.1.6). The first role is the output language of compilers. A *compiler* translates a program written in a

assembler directive An operation that tells the assembler how to translate a program but does not produce machine instructions; always begins with a period.

```

addiu

$29, $29, -32

SW

$31, 20($29)

SW

$4, 32($29)

$5, 36($29)

SW

$0, 24($29)

SW

SW

$0, 28($29)

$14, 28($29)

1 w

٦w

$24, 24($29)

multu

$14, $14

addiu

$8, $14, 1

slti

$1, $8, 101

$8,

28($29)

SW

mflo

$15

$25, $24, $15

addu

$1, $0, -9

$25, 24($29)

bne

SW

$4, 4096

lui

24($29)

1 w

$5,

1048812

.ial

addiu

$4, $4, 1072

$31, 20($29)

1 w

addiu

$29, $29, 32

jr

$31

move

$2,

$0

```

**FIGURE A.1.3** The same routine written in assembly language. However, the code for the routine does not label registers or memory locations nor include comments.

**source language** The highlevel language in which a program is originally written. high-level language (such as C or Pascal) into an equivalent program in machine or assembly language. The high-level language is called the **source language**, and the compiler's output is its *target language*.

Assembly language's other role is as a language in which to write programs. This role used to be the dominant one. Today, however, because of larger main memories and better compilers, most programmers write in a high-level language and rarely, if ever, see the instructions that a computer executes. Nevertheless, assembly language is still important to write programs in which speed or size are critical or to exploit hardware features that have no analogues in high-level languages.

Although this appendix focuses on MIPS assembly language, assembly programming on most other machines is very similar. The additional instructions and address modes in CISC machines, such as the VAX, can make assembly programs shorter but do not change the process of assembling a program or provide assembly language with the advantages of high-level languages such as type-checking and structured control flow.

A.1 Introduction A-7

```

.text

2

.align

.globl

main

main:

subu

$sp, $sp, 32

$ra, 20($sp)

SW

sd

$a0, 32($sp)

$0, 24($sp)

$0, 28($sp)

SW

SW

loop:

1 w

$t6, 28($sp)

mu1

$t7, $t6, $t6

l w

$t8, 24($sp)

$t9, $t8, $t7

addu

$t9, 24($sp)

SW

addu

$t0, $t6, 1

$t0, 28($sp)

SW

$t0, 100, loop

ble

1 a

$a0, str

$a1, 24($sp)

1 w

jal

printf

move

$v0, $0

$ra, 20($sp)

l w

addu

$sp, $sp, 32

jr

$ra

.data

.align

str:

.asciiz

"The sum from 0 .. 100 is %d\n"

```

**FIGURE A.1.4** The same routine written in assembly language with labels, but no comments. The commands that start with periods are assembler directives (see pages A-47–A-49). .text indicates that succeeding lines contain instructions. .data indicates that they contain data. .align n indicates that the items on the succeeding lines should be aligned on a  $2^n$  byte boundary. Hence, .align 2 means the next item should be on a word boundary. .globl main declares that main is a global symbol that should be visible to code stored in other files. Finally, .asciiz stores a null-terminated string in memory.

## When to Use Assembly Language

The primary reason to program in assembly language, as opposed to an available high-level language, is that the speed or size of a program is critically important. For example, consider a computer that controls a piece of machinery, such as a car's brakes. A computer that is incorporated in another device, such as a car, is called an *embedded computer*. This type of computer needs to respond rapidly and predictably to events in the outside world. Because a compiler introduces uncer-

```

#include <stdio.h>

int

main (int argc, char *argv[])

{

int i;

int sum = 0;

for (i = 0; i <= 100; i = i + 1) sum = sum + i * i;

printf ("The sum from 0 .. 100 is %d\n", sum);

}</pre>

```

FIGURE A.1.5 The routine written in the C programming language.

FIGURE A.1.6 Assembly language either is written by a programmer or is the output of a compiler.

tainty about the time cost of operations, programmers may find it difficult to ensure that a high-level language program responds within a definite time interval—say, 1 millisecond after a sensor detects that a tire is skidding. An assembly language programmer, on the other hand, has tight control over which instructions execute. In addition, in embedded applications, reducing a program's size, so that it fits in fewer memory chips, reduces the cost of the embedded computer.

A hybrid approach, in which most of a program is written in a high-level language and time-critical sections are written in assembly language, builds on the strengths of both languages. Programs typically spend most of their time executing a small fraction of the program's source code. This observation is just the principle of locality that underlies caches (see Section 7.2 in Chapter 7).

Program profiling measures where a program spends its time and can find the time-critical parts of a program. In many cases, this portion of the program can be made faster with better data structures or algorithms. Sometimes, however, significant performance improvements only come from recoding a critical portion of a program in assembly language.

A.1 Introduction A-9

This improvement is not necessarily an indication that the high-level language's compiler has failed. Compilers typically are better than programmers at producing uniformly high-quality machine code across an entire program. Programmers, however, understand a program's algorithms and behavior at a deeper level than a compiler and can expend considerable effort and ingenuity improving small sections of the program. In particular, programmers often consider several procedures simultaneously while writing their code. Compilers typically compile each procedure in isolation and must follow strict conventions governing the use of registers at procedure boundaries. By retaining commonly used values in registers, even across procedure boundaries, programmers can make a program run faster.

Another major advantage of assembly language is the ability to exploit specialized instructions, for example, string copy or pattern-matching instructions. Compilers, in most cases, cannot determine that a program loop can be replaced by a single instruction. However, the programmer who wrote the loop can replace it easily with a single instruction.

Currently, a programmer's advantage over a compiler has become difficult to maintain as compilation techniques improve and machines' pipelines increase in complexity (Chapter 6).

The final reason to use assembly language is that no high-level language is available on a particular computer. Many older or specialized computers do not have a compiler, so a programmer's only alternative is assembly language.

### **Drawbacks of Assembly Language**

Assembly language has many disadvantages that strongly argue against its widespread use. Perhaps its major disadvantage is that programs written in assembly language are inherently machine-specific and must be totally rewritten to run on another computer architecture. The rapid evolution of computers discussed in Chapter 1 means that architectures become obsolete. An assembly language program remains tightly bound to its original architecture, even after the computer is eclipsed by new, faster, and more cost-effective machines.

Another disadvantage is that assembly language programs are longer than the equivalent programs written in a high-level language. For example, the C program in Figure A.1.5 is 11 lines long, while the assembly program in Figure A.1.4 is 31 lines long. In more complex programs, the ratio of assembly to high-level language (its *expansion factor*) can be much larger than the factor of three in this example. Unfortunately, empirical studies have shown that programmers write roughly the same number of lines of code per day in assembly as in high-level languages. This means that programmers are roughly *x* times more productive in a high-level language, where *x* is the assembly language expansion factor.

To compound the problem, longer programs are more difficult to read and understand and they contain more bugs. Assembly language exacerbates the problem because of its complete lack of structure. Common programming idioms, such as *if-then* statements and loops, must be built from branches and jumps. The resulting programs are hard to read because the reader must reconstruct every higher-level construct from its pieces and each instance of a statement may be slightly different. For example, look at Figure A.1.4 and answer these questions: What type of loop is used? What are its lower and upper bounds?

**Elaboration:** Compilers can produce machine language directly instead of relying on an assembler. These compilers typically execute much faster than those that invoke an assembler as part of compilation. However, a compiler that generates machine language must perform many tasks that an assembler normally handles, such as resolving addresses and encoding instructions as binary numbers. The trade-off is between compilation speed and compiler simplicity.

**Elaboration:** Despite these considerations, some embedded applications are written in a high-level language. Many of these applications are large and complex programs that must be extremely reliable. Assembly language programs are longer and more difficult to write and read than high-level language programs. This greatly increases the cost of writing an assembly language program and makes it extremely difficult to verify the correctness of this type of program. In fact, these considerations led the Department of Defense, which pays for many complex embedded systems, to develop Ada, a new high-level language for writing embedded systems.

# A.2

### **Assemblers**

external label Also called global label. A label referring to an object that can be referenced from files other than the one in which it is defined.

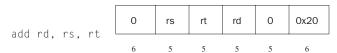

**local label** A label referring to an object that can be used only within the file in which it is defined. An assembler translates a file of assembly language statements into a file of binary machine instructions and binary data. The translation process has two major parts. The first step is to find memory locations with labels so the relationship between symbolic names and addresses is known when instructions are translated. The second step is to translate each assembly statement by combining the numeric equivalents of opcodes, register specifiers, and labels into a legal instruction. As shown in Figure A.1.1, the assembler produces an output file, called an *object file*, which contains the machine instructions, data, and bookkeeping information.

An object file typically cannot be executed because it references procedures or data in other files. A **label** is **external** (also called **global**) if the labeled object can

A.2 Assemblers A-11

be referenced from files other than the one in which it is defined. A label is *local* if the object can be used only within the file in which it is defined. In most assemblers, labels are local by default and must be explicitly declared global. Subroutines and global variables require external labels since they are referenced from many files in a program. **Local labels** hide names that should not be visible to other modules—for example, static functions in C, which can only be called by other functions in the same file. In addition, compiler-generated names—for example, a name for the instruction at the beginning of a loop—are local so the compiler need not produce unique names in every file.

#### **Local and Global Labels**

Consider the program in Figure A.1.4 on page A-7. The subroutine has an external (global) label main. It also contains two local labels—loop and str—that are only visible with this assembly language file. Finally, the routine also contains an unresolved reference to an external label printf, which is the library routine that prints values. Which labels in Figure A.1.4 could be referenced from another file?

Only global labels are visible outside of a file, so the only label that could be referenced from another file is main.

Since the assembler processes each file in a program individually and in isolation, it only knows the addresses of local labels. The assembler depends on another tool, the linker, to combine a collection of object files and libraries into an executable file by resolving external labels. The assembler assists the linker by providing lists of labels and unresolved references.

However, even local labels present an interesting challenge to an assembler. Unlike names in most high-level languages, assembly labels may be used before they are defined. In the example, in Figure A.1.4, the label str is used by the la instruction before it is defined. The possibility of a **forward reference**, like this one, forces an assembler to translate a program in two steps: first find all labels and then produce instructions. In the example, when the assembler sees the la instruction, it does not know where the word labeled str is located or even whether str labels an instruction or datum.

**EXAMPLE**

**ANSWER**

**forward reference** A label that is used before it is defined.

An assembler's first pass reads each line of an assembly file and breaks it into its component pieces. These pieces, which are called *lexemes*, are individual words, numbers, and punctuation characters. For example, the line

contains six lexemes: the opcode ble, the register specifier \$t0, a comma, the number 100, a comma, and the symbol loop.

If a line begins with a label, the assembler records in its **symbol table** the name of the label and the address of the memory word that the instruction occupies. The assembler then calculates how many words of memory the instruction on the current line will occupy. By keeping track of the instructions' sizes, the assembler can determine where the next instruction goes. To compute the size of a variable-length instruction, like those on the VAX, an assembler has to examine it in detail. Fixed-length instructions, like those on MIPS, on the other hand, require only a cursory examination. The assembler performs a similar calculation to compute the space required for data statements. When the assembler reaches the end of an assembly file, the symbol table records the location of each label defined in the file.

The assembler uses the information in the symbol table during a second pass over the file, which actually produces machine code. The assembler again examines each line in the file. If the line contains an instruction, the assembler combines the binary representations of its opcode and operands (register specifiers or memory address) into a legal instruction. The process is similar to the one used in Section 2.4 in Chapter 2. Instructions and data words that reference an external symbol defined in another file cannot be completely assembled (they are unresolved) since the symbol's address is not in the symbol table. An assembler does not complain about unresolved references since the corresponding label is likely to be defined in another file

The **BIG**Picture

Assembly language is a programming language. Its principal difference from high-level languages such as BASIC, Java, and C is that assembly language provides only a few, simple types of data and control flow. Assembly language programs do not specify the type of value held in a variable. Instead, a programmer must apply the appropriate operations (e.g., integer or floating-point addition) to a value. In addition, in assembly language, programs must implement all control flow with *go tos*. Both factors make assembly language programming for any machine—MIPS or 80x86—more difficult and error-prone than writing in a high-level language.

**symbol table** A table that matches names of labels to the addresses of the memory words that instructions occupy.

A.2 Assemblers A-13

**Elaboration:** If an assembler's speed is important, this two-step process can be done in one pass over the assembly file with a technique known as backpatching. In its pass over the file, the assembler builds a (possibly incomplete) binary representation of every instruction. If the instruction references a label that has not yet been defined, the assembler records the label and instruction in a table. When a label is defined, the assembler consults this table to find all instructions that contain a forward reference to the label. The assembler goes back and corrects their binary representation to incorporate the address of the label. Backpatching speeds assembly because the assembler only reads its input once. However, it requires an assembler to hold the entire binary representation of a program in memory so instructions can be backpatched. This requirement can limit the size of programs that can be assembled. The process is complicated by machines with several types of branches that span different ranges of instructions. When the assembler first sees an unresolved label in a branch instruction, it must either use the largest possible branch or risk having to go back and readjust many instructions to make room for a larger branch.

backpatching A method for translating from assembly language to machine instructions in which the assembler builds a (possibly incomplete) binary representation of every instruction in one pass over a program and then returns to fill in previously undefined labels.

# **Object File Format**

Assemblers produce object files. An object file on UNIX contains six distinct sections (see Figure A.2.1):

- The *object file header* describes the size and position of the other pieces of the file.

- The **text segment** contains the machine language code for routines in the source file. These routines may be unexecutable because of unresolved references.

- The **data segment** contains a binary representation of the data in the source file. The data also may be incomplete because of unresolved references to labels in other files.

- The **relocation information** identifies instructions and data words that depend on **absolute addresses**. These references must change if portions of the program are moved in memory.

- The *symbol table* associates addresses with external labels in the source file and lists unresolved references.

- The *debugging information* contains a concise description of the way in which the program was compiled, so a debugger can find which instruction addresses correspond to lines in a source file and print the data structures in readable form.

The assembler produces an object file that contains a binary representation of the program and data and additional information to help link pieces of a pro**text segment** The segment of a UNIX object file that contains the machine language code for routines in the source file.

**data segment** The segment of a UNIX object or executable file that contains a binary representation of the initialized data used by the program.

relocation information The segment of a UNIX object file that identifies instructions and data words that depend on absolute addresses.

**absolute address** A variable's or routine's actual address in memory.

| Object file header | Text<br>segment | Data<br>segment | Relocation information | Symbol table | Debugging information |

|--------------------|-----------------|-----------------|------------------------|--------------|-----------------------|

|--------------------|-----------------|-----------------|------------------------|--------------|-----------------------|

**FIGURE A.2.1 Object file.** A UNIX assembler produces an object file with six distinct sections.

gram. This relocation information is necessary because the assembler does not know which memory locations a procedure or piece of data will occupy after it is linked with the rest of the program. Procedures and data from a file are stored in a contiguous piece of memory, but the assembler does not know where this memory will be located. The assembler also passes some symbol table entries to the linker. In particular, the assembler must record which external symbols are defined in a file and what unresolved references occur in a file.

**Elaboration:** For convenience, assemblers assume each file starts at the same address (for example, location 0) with the expectation that the linker will *relocate* the code and data when they are assigned locations in memory. The assembler produces *relocation information*, which contains an entry describing each instruction or data word in the file that references an absolute address. On MIPS, only the subroutine call, load, and store instructions reference absolute addresses. Instructions that use PC-relative addressing, such as branches, need not be relocated.

#### **Additional Facilities**

Assemblers provide a variety of convenience features that help make assembler programs short and easier to write, but do not fundamentally change assembly language. For example, *data layout directives* allow a programmer to describe data in a more concise and natural manner than its binary representation.

In Figure A.1.4, the directive

```

.asciiz "The sum from 0 .. 100 is %d\n"

```

stores characters from the string in memory. Contrast this line with the alternative of writing each character as its ASCII value (Figure 2.21 in Chapter 2 describes the ASCII encoding for characters):

```

.byte 84, 104, 101, 32, 115, 117, 109, 32

.byte 102, 114, 111, 109, 32, 48, 32, 46

.byte 46, 32, 49, 48, 48, 32, 105, 115

.byte 32, 37, 100, 10, 0

```

The .asciiz directive is easier to read because it represents characters as letters, not binary numbers. An assembler can translate characters to their binary representation much faster and more accurately than a human. Data layout directives

A.2 Assemblers A-15

specify data in a human-readable form that the assembler translates to binary. Other layout directives are described in Section A.10 on page A-45.

#### **String Directive**

Define the sequence of bytes produced by this directive:

```

.asciiz "The quick brown fox jumps over the lazy dog"

```

```

.byte 84, 104, 101, 32, 113, 117, 105, 99

.byte 107, 32, 98, 114, 111, 119, 110, 32

.byte 102, 111, 120, 32, 106, 117, 109, 112

.byte 115, 32, 111, 118, 101, 114, 32, 116

.byte 104, 101, 32, 108, 97, 122, 121, 32

.byte 100, 111, 103, 0

```

Macros are a pattern-matching and replacement facility that provide a simple mechanism to name a frequently used sequence of instructions. Instead of repeatedly typing the same instructions every time they are used, a programmer invokes the macro and the assembler replaces the macro call with the corresponding sequence of instructions. Macros, like subroutines, permit a programmer to create and name a new abstraction for a common operation. Unlike subroutines, however, macros do not cause a subroutine call and return when the program runs since a macro call is replaced by the macro's body when the program is assembled. After this replacement, the resulting assembly is indistinguishable from the equivalent program written without macros.

### **Macros**

As an example, suppose that a programmer needs to print many numbers. The library routine printf accepts a format string and one or more values to print as its arguments. A programmer could print the integer in register \$7 with the following instructions:

**EXAMPLE**

**ANSWER**

**EXAMPLE**

```

mov $a1, $7 # Load value into

# second arg

jal printf # Call the printf routine

```

The .data directive tells the assembler to store the string in the program's data segment, and the .text directive tells the assembler to store the instructions in its text segment.

However, printing many numbers in this fashion is tedious and produces a verbose program that is difficult to understand. An alternative is to introduce a macro, print\_int, to print an integer:

The macro has a **formal parameter**, <code>\$arg</code>, that names the argument to the macro. When the macro is expanded, the argument from a call is substituted for the formal parameter throughout the macro's body. Then the assembler replaces the call with the macro's newly expanded body. In the first call on <code>print\_int</code>, the argument is \$7, so the macro expands to the code

```

la $a0, int_str

mov $a1, $7

jal printf

```

In a second call on print\_int, say, print\_int(\$t0), the argument is \$t0, so the macro expands to

```

la $a0, int_str

mov $a1, $t0

jal printf

```

What does the call print\_int(\$a0) expand to?

**formal parameter** A variable that is the argument to a procedure or macro; replaced by that argument once the macro is expanded.

A.2 Assemblers A-17

```

la $a0, int_str

mov $a1, $a0

jal printf

```

**ANSWER**

This example illustrates a drawback of macros. A programmer who uses this macro must be aware that print\_int uses register \$a0 and so cannot correctly print the value in that register.

Some assemblers also implement *pseudoinstructions*, which are instructions provided by an assembler but not implemented in hardware. Chapter 2 contains many examples of how the MIPS assembler synthesizes pseudoinstructions and addressing modes from the spartan MIPS hardware instruction set. For example, Section 2.6 in Chapter 2 describes how the assembler synthesizes the blt instruction from two other instructions: slt and bne. By extending the instruction set, the MIPS assembler makes assembly language programming easier without complicating the hardware. Many pseudoinstructions could also be simulated with macros, but the MIPS assembler can generate better code for these instructions because it can use a dedicated register (\$at) and is able to optimize the generated code.

Hardware Software Interface

**Elaboration:** Assemblers *conditionally assemble* pieces of code, which permits a programmer to include or exclude groups of instructions when a program is assembled. This feature is particularly useful when several versions of a program differ by a small amount. Rather than keep these programs in separate files—which greatly complicates fixing bugs in the common code—programmers typically merge the versions into a single file. Code particular to one version is conditionally assembled, so it can be excluded when other versions of the program are assembled.

If macros and conditional assembly are useful, why do assemblers for UNIX systems rarely, if ever, provide them? One reason is that most programmers on these systems write programs in higher-level languages like C. Most of the assembly code is produced by compilers, which find it more convenient to repeat code rather than define macros. Another reason is that other tools on UNIX—such as cpp, the C preprocessor, or m4, a general macro processor—can provide macros and conditional assembly for assembly language programs.

# **A.3**

#### Linkers

separate compilation Splitting a program across many files, each of which can be compiled without knowledge of what is in the other files.

**Separate compilation** permits a program to be split into pieces that are stored in different files. Each file contains a logically related collection of subroutines and data structures that form a *module* in a larger program. A file can be compiled and assembled independently of other files, so changes to one module do not require recompiling the entire program. As we discussed above, separate compilation necessitates the additional step of linking to combine object files from separate modules and fix their unresolved references.

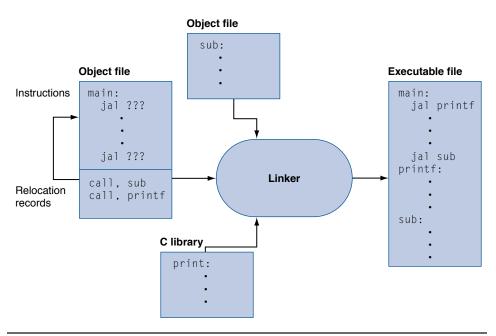

The tool that merges these files is the *linker* (see Figure A.3.1). It performs three tasks:

- Searches the program libraries to find library routines used by the program

- Determines the memory locations that code from each module will occupy and relocates its instructions by adjusting absolute references

- Resolves references among files

A linker's first task is to ensure that a program contains no undefined labels. The linker matches the external symbols and unresolved references from a program's files. An external symbol in one file resolves a reference from another file if both refer to a label with the same name. Unmatched references mean a symbol was used, but not defined anywhere in the program.

Unresolved references at this stage in the linking process do not necessarily mean a programmer made a mistake. The program could have referenced a library routine whose code was not in the object files passed to the linker. After matching symbols in the program, the linker searches the system's program libraries to find predefined subroutines and data structures that the program references. The basic libraries contain routines that read and write data, allocate and deallocate memory, and perform numeric operations. Other libraries contain routines to access a database or manipulate terminal windows. A program that references an unresolved symbol that is not in any library is erroneous and cannot be linked. When the program uses a library routine, the linker extracts the routine's code from the library and incorporates it into the program text segment. This new routine, in turn, may depend on other library routines, so the linker continues to fetch other library routines until no external references are unresolved or a routine cannot be found.

If all external references are resolved, the linker next determines the memory locations that each module will occupy. Since the files were assembled in isolation,

A.4 Loading A-19

FIGURE A.3.1 The linker searches a collection of object files and program libraries to find nonlocal routines used in a program, combines them into a single executable file, and resolves references between routines in different files.

the assembler could not know where a module's instructions or data will be placed relative to other modules. When the linker places a module in memory, all absolute references must be *relocated* to reflect its true location. Since the linker has relocation information that identifies all relocatable references, it can efficiently find and backpatch these references.

The linker produces an executable file that can run on a computer. Typically, this file has the same format as an object file, except that it contains no unresolved references or relocation information.

# Loading

A program that links without an error can be run. Before being run, the program resides in a file on secondary storage, such as a disk. On UNIX systems, the oper-

ating system kernel brings a program into memory and starts it running. To start a program, the operating system performs the following steps:

- 1. Reads the executable file's header to determine the size of the text and data segments.

- 2. Creates a new address space for the program. This address space is large enough to hold the text and data segments, along with a stack segment (see Section A.5).

- 3. Copies instructions and data from the executable file into the new address space.

- 4. Copies arguments passed to the program onto the stack.

- 5. Initializes the machine registers. In general, most registers are cleared, but the stack pointer must be assigned the address of the first free stack location (see Section A.5).

- 6. Jumps to a start-up routine that copies the program's arguments from the stack to registers and calls the program's main routine. If the main routine returns, the start-up routine terminates the program with the exit system call.

# **A.5**

# **Memory Usage**

The next few sections elaborate the description of the MIPS architecture presented earlier in the book. Earlier chapters focused primarily on hardware and its relationship with low-level software. These sections focus primarily on how assembly language programmers use MIPS hardware. These sections describe a set of conventions followed on many MIPS systems. For the most part, the hardware does not impose these conventions. Instead, they represent an agreement among programmers to follow the same set of rules so that software written by different people can work together and make effective use of MIPS hardware.

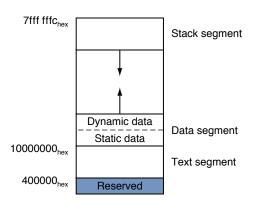

Systems based on MIPS processors typically divide memory into three parts (see Figure A.5.1). The first part, near the bottom of the address space (starting at address 400000<sub>bex</sub>), is the *text segment*, which holds the program's instructions.

The second part, above the text segment, is the *data segment*, which is further divided into two parts. **Static data** (starting at address  $10000000_{hex}$ ) contains objects whose size is known to the compiler and whose lifetime—the interval during which a program can access them—is the program's entire execution. For example, in C, global variables are statically allocated since they can be referenced

static data The portion of memory that contains data whose size is known to the compiler and whose lifetime is the program's entire execution. A.5 Memory Usage A-21

FIGURE A.5.1 Layout of memory.

Because the data segment begins far above the program at address  $10000000_{hex}$ , load and store instructions cannot directly reference data objects with their 16-bit offset fields (see Section 2.4 in Chapter 2). For example, to load the word in the data segment at address  $10010020_{hex}$  into register \$v0 requires two instructions:

# Hardware Software Interface

```

lui $s0, 0x1001 \# 0x1001 means 1001 base 16 lw $v0, 0x0020($s0) \# 0x10010000 + 0x0020 = 0x10010020

```

(The 0x before a number means that it is a hexadecimal value. For example,  $0\times8000$  is  $8000_{\text{hex}}$  or  $32,768_{\text{ten}}$ .)

To avoid repeating the <code>lui</code> instruction at every load and store, MIPS systems typically dedicate a register (<code>\$gp</code>) as a *global pointer* to the static data segment. This register contains address <code>10008000\_hex</code>, so load and store instructions can use their signed <code>16-bit</code> offset fields to access the first 64 KB of the static data segment. With this global pointer, we can rewrite the example as a single instruction:

```

1w $v0, 0x8020($gp)

```

Of course, a global pointer register makes addressing locations  $10000000_{\rm hex}-10010000_{\rm hex}$  faster than other heap locations. The MIPS compiler usually stores *global variables* in this area because these variables have fixed locations and fit better than other global data, such as arrays.

anytime during a program's execution. The linker both assigns static objects to locations in the data segment and resolves references to these objects.

Immediately above static data is *dynamic data*. This data, as its name implies, is allocated by the program as it executes. In C programs, the malloc library routine finds and returns a new block of memory. Since a compiler cannot predict how much memory a program will allocate, the operating system expands the dynamic data area to meet demand. As the upward arrow in the figure indicates, malloc expands the dynamic area with the sbrk system call, which causes the operating system to add more pages to the program's virtual address space (see Section 7.4 in Chapter 7) immediately above the dynamic data segment.

The third part, the program **stack segment**, resides at the top of the virtual address space (starting at address 7fffffff<sub>hex</sub>). Like dynamic data, the maximum size of a program's stack is not known in advance. As the program pushes values on the stack, the operating system expands the stack segment down, toward the data segment.

This three-part division of memory is not the only possible one. However, it has two important characteristics: the two dynamically expandable segments are as far apart as possible, and they can grow to use a program's entire address space.

**stack segment** The portion of memory used by a program to hold procedure call frames.

# **A.6**

## **Procedure Call Convention**

Conventions governing the use of registers are necessary when procedures in a program are compiled separately. To compile a particular procedure, a compiler must know which registers it may use and which registers are reserved for other procedures. Rules for using registers are called **register use** or **procedure call conventions**. As the name implies, these rules are, for the most part, conventions followed by software rather than rules enforced by hardware. However, most compilers and programmers try very hard to follow these conventions because violating them causes insidious bugs.

The calling convention described in this section is the one used by the gcc compiler. The native MIPS compiler uses a more complex convention that is slightly faster.

The MIPS CPU contains 32 general-purpose registers that are numbered 0–31. Register \$0 always contains the hardwired value 0.

- Registers \$at (1), \$k0 (26), and \$k1 (27) are reserved for the assembler and operating system and should not be used by user programs or compilers.

- Registers \$a0-\$a3 (4-7) are used to pass the first four arguments to routines (remaining arguments are passed on the stack). Registers \$v0 and \$v1 (2, 3) are used to return values from functions.

register-use convention Also called procedure call convention. A software protocol governing the use of registers by procedures.

■ Registers \$t0-\$t9 (8-15, 24, 25) are **caller-saved registers** that are used to hold temporary quantities that need not be preserved across calls (see Section 2.7 in Chapter 2).

- Registers \$\$0-\$\$7 (16-23) are **callee-saved registers** that hold long-lived values that should be preserved across calls.

- Register \$gp (28) is a global pointer that points to the middle of a 64K block of memory in the static data segment.

- Register \$sp (29) is the stack pointer, which points to the last location on the stack. Register \$fp (30) is the frame pointer. The jal instruction writes register \$ra (31), the return address from a procedure call. These two registers are explained in the next section.

The two-letter abbreviations and names for these registers—for example, \$sp for the stack pointer—reflect the registers' intended uses in the procedure call convention. In describing this convention, we will use the names instead of register numbers. Figure A.6.1 lists the registers and describes their intended uses.

#### **Procedure Calls**

This section describes the steps that occur when one procedure (the *caller*) invokes another procedure (the *callee*). Programmers who write in a high-level language (like C or Pascal) never see the details of how one procedure calls another because the compiler takes care of this low-level bookkeeping. However, assembly language programmers must explicitly implement every procedure call and return.

Most of the bookkeeping associated with a call is centered around a block of memory called a **procedure call frame**. This memory is used for a variety of purposes:

- To hold values passed to a procedure as arguments

- To save registers that a procedure may modify, but which the procedure's caller does not want changed

- To provide space for variables local to a procedure

In most programming languages, procedure calls and returns follow a strict last-in, first-out (LIFO) order, so this memory can be allocated and deallocated on a stack, which is why these blocks of memory are sometimes called stack frames.

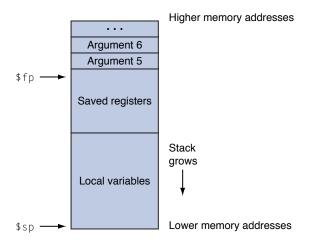

Figure A.6.2 shows a typical stack frame. The frame consists of the memory between the frame pointer (\$fp), which points to the first word of the frame, and the stack pointer (\$sp), which points to the last word of the frame. The stack grows down from higher memory addresses, so the frame pointer points above

**caller-saved register** A register saved by the routine being called.

**callee-saved register** A register saved by the routine making a procedure call.

procedure call frame A block of memory that is used to hold values passed to a procedure as arguments, to save registers that a procedure may modify but that the procedure's caller does not want changed, and to provide space for variables local to a procedure.

| Register name | Number | Usage                                           |  |

|---------------|--------|-------------------------------------------------|--|

| \$zero        | 0      | constant 0                                      |  |

| \$at          | 1      | reserved for assembler                          |  |

| \$ v 0        | 2      | expression evaluation and results of a function |  |

| \$v1          | 3      | expression evaluation and results of a function |  |

| \$a0          | 4      | argument 1                                      |  |

| \$a1          | 5      | argument 2                                      |  |

| \$a2          | 6      | argument 3                                      |  |

| \$a3          | 7      | argument 4                                      |  |

| \$t0          | 8      | temporary (not preserved across call)           |  |

| \$t1          | 9      | temporary (not preserved across call)           |  |

| \$t2          | 10     | temporary (not preserved across call)           |  |

| \$t3          | 11     | temporary (not preserved across call)           |  |

| \$t4          | 12     | temporary (not preserved across call)           |  |

| \$t5          | 13     | temporary (not preserved across call)           |  |

| \$t6          | 14     | temporary (not preserved across call)           |  |

| \$t7          | 15     | temporary (not preserved across call)           |  |

| \$s0          | 16     | saved temporary (preserved across call)         |  |

| \$s1          | 17     | saved temporary (preserved across call)         |  |

| \$s2          | 18     | saved temporary (preserved across call)         |  |

| \$s3          | 19     | saved temporary (preserved across call)         |  |

| \$s4          | 20     | saved temporary (preserved across call)         |  |

| \$s5          | 21     | saved temporary (preserved across call)         |  |

| \$s6          | 22     | saved temporary (preserved across call)         |  |

| \$s7          | 23     | saved temporary (preserved across call)         |  |

| \$t8          | 24     | temporary (not preserved across call)           |  |

| \$t9          | 25     | temporary (not preserved across call)           |  |

| \$k0          | 26     | reserved for OS kernel                          |  |

| \$k1          | 27     | reserved for OS kernel                          |  |

| \$gp          | 28     | pointer to global area                          |  |

| \$sp          | 29     | stack pointer                                   |  |

| \$fp          | 30     | frame pointer                                   |  |

| \$ra          | 31     | return address (used by function call)          |  |

FIGURE A.6.1 MIPS registers and usage convention.

the stack pointer. The executing procedure uses the frame pointer to quickly access values in its stack frame. For example, an argument in the stack frame can be loaded into register  $\$ \lor 0$  with the instruction

lw \$v0, 0(\$fp)

**FIGURE A.6.2 Layout of a stack frame.** The frame pointer (\$fp) points to the first word in the currently executing procedure's stack frame. The stack pointer (\$sp) points to the last word of frame. The first four arguments are passed in registers, so the fifth argument is the first one stored on the stack.

A stack frame may be built in many different ways; however, the caller and callee must agree on the sequence of steps. The steps below describe the calling convention used on most MIPS machines. This convention comes into play at three points during a procedure call: immediately before the caller invokes the callee, just as the callee starts executing, and immediately before the callee returns to the caller. In the first part, the caller puts the procedure call arguments in standard places and invokes the callee to do the following:

- 1. Pass arguments. By convention, the first four arguments are passed in registers \$a0-\$a3. Any remaining arguments are pushed on the stack and appear at the beginning of the called procedure's stack frame.

- 2. Save caller-saved registers. The called procedure can use these registers (\$a0-\$a3 and \$t0-\$t9) without first saving their value. If the caller expects to use one of these registers after a call, it must save its value before the call.

- 3. Execute a jal instruction (see Section 2.7 of Chapter 2), which jumps to the callee's first instruction and saves the return address in register \$ra.

Before a called routine starts running, it must take the following steps to set up its stack frame:

- 1. Allocate memory for the frame by subtracting the frame's size from the stack pointer.

- 2. Save callee-saved registers in the frame. A callee must save the values in these registers (\$\$0-\$\$7, \$fp, and \$ra) before altering them since the caller expects to find these registers unchanged after the call. Register \$fp is saved by every procedure that allocates a new stack frame. However, register \$ra only needs to be saved if the callee itself makes a call. The other callee-saved registers that are used also must be saved.

- 3. Establish the frame pointer by adding the stack frame's size minus 4 to \$sp and storing the sum in register \$fp.

# Hardware Software Interface

The MIPS register use convention provides callee- and caller-saved registers because both types of registers are advantageous in different circumstances. Callee-saved registers are better used to hold long-lived values, such as variables from a user's program. These registers are only saved during a procedure call if the callee expects to use the register. On the other hand, caller-saved registers are better used to hold short-lived quantities that do not persist across a call, such as immediate values in an address calculation. During a call, the callee can also use these registers for short-lived temporaries.

Finally, the callee returns to the caller by executing the following steps:

- 1. If the callee is a function that returns a value, place the returned value in register \$v0.

- 2. Restore all callee-saved registers that were saved upon procedure entry.

- 3. Pop the stack frame by adding the frame size to \$sp.

- 4. Return by jumping to the address in register \$ra.

#### recursive procedures

Procedures that call themselves either directly or indirectly through a chain of calls.

**Elaboration:** A programming language that does not permit recursive procedures—procedures that call themselves either directly or indirectly through a chain of calls—need not allocate frames on a stack. In a nonrecursive language, each procedure's frame may be statically allocated since only one invocation of a procedure can be active at a time. Older versions of Fortran prohibited recursion because statically allocated frames produced faster code on some older machines. However, on load-store architectures like MIPS, stack frames may be just as fast because a frame pointer register points directly to

the active stack frame, which permits a single load or store instruction to access values in the frame. In addition, recursion is a valuable programming technique.

### **Procedure Call Example**

As an example, consider the C routine

```

main ()

{

printf ("The factorial of 10 is %d\n", fact (10));

}

int fact (int n)

{

if (n < 1)

return (1);

else

return (n * fact (n - 1));

}</pre>

```

which computes and prints 10! (the factorial of 10,  $10! = 10 \times 9 \times ... \times 1$ ). fact is a recursive routine that computes n! by multiplying n times (n-1)!. The assembly code for this routine illustrates how programs manipulate stack frames.

Upon entry, the routine main creates its stack frame and saves the two calleesaved registers it will modify: \$fp and \$ra. The frame is larger than required for these two registers because the calling convention requires the minimum size of a stack frame to be 24 bytes. This minimum frame can hold four argument registers (\$a0-\$a3) and the return address \$ra, padded to a double-word boundary (24 bytes). Since main also needs to save \$fp, its stack frame must be two words larger (remember: the stack pointer is kept doubleword aligned).

The routine main then calls the factorial routine and passes it the single argument 10. After fact returns, main calls the library routine printf and passes it both a format string and the result returned from fact:

```

li $a0,10  # Put argument (10) in $a0 jal fact # Call factorial function

la $a0,$LC  # Put format string in $a0 move $a1,$v0  # Move fact result to $a1 jal printf # Call the print function

```

Finally, after printing the factorial, main returns. But first, it must restore the registers it saved and pop its stack frame:

```

1 w

$ra,20($sp)

# Restore return address

$fp,16($sp)

٦w

# Restore frame pointer

# Pop stack frame

addiu

$sp,$sp,32

jr

$ra

# Return to caller

.rdata

$LC:

.ascii

"The factorial of 10 is %d\n\000"

```

The factorial routine is similar in structure to main. First, it creates a stack frame and saves the callee-saved registers it will use. In addition to saving \$ra and \$fp, fact also saves its argument (\$a0), which it will use for the recursive call:

```

.text

fact:

# Stack frame is 32 bytes long

subu

$sp.$sp.32

$ra,20($sp)

# Save return address

SW

$fp,16($sp)

# Save frame pointer

SW

# Set up frame pointer

$fp,$sp,28

addiu

$a0.0($fp)

# Save argument (n)

SW

```

The heart of the fact routine performs the computation from the C program. It tests if the argument is greater than 0. If not, the routine returns the value 1. If the argument is greater than 0, the routine recursively calls itself to compute fact(n-1) and multiplies that value times n:

```

$v0,0($fp)

# Load n

٦w

bqtz

$v0,$L2

\# Branch if n > 0

lί

$v0.1

# Return 1

$11

# Jump to code to return

jr

$L2:

$v1,0($fp)

# Load n

subu

$v0,$v1,1

# Compute n - 1

# Move value to $a0

move

$a0,$v0

```

```

jal fact \# Call factorial function

lw \$v1,0(\$fp) \# Load n

mul \$v0,\$v0,\$v1 \# Compute fact(n-1) * n

```

Finally, the factorial routine restores the callee-saved registers and returns the value in register \$ \( \psi \):

#### **Stack in Recursive Procedure**

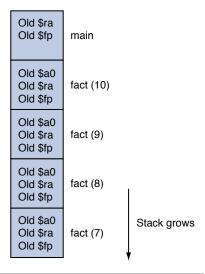

Figure A.6.3 shows the stack at the call fact(7). main runs first, so its frame is deepest on the stack. main calls fact(10), whose stack frame is next on the stack. Each invocation recursively invokes fact to compute the next-lowest factorial. The stack frames parallel the LIFO order of these calls. What does the stack look like when the call to fact(10) returns?

# **EXAMPLE**

FIGURE A.6.3 Stack frames during the call of fact(7).

# **ANSWER**

**Elaboration:** The difference between the MIPS compiler and the gcc compiler is that the MIPS compiler usually does not use a frame pointer, so this register is available as another callee-saved register, \$s8. This change saves a couple of instructions in the procedure call and return sequence. However, it complicates code generation because a procedure must access its stack frame with \$sp, whose value can change during a procedure's execution if values are pushed on the stack.

### **Another Procedure Call Example**

As another example, consider the following routine that computes the tak function, which is a widely used benchmark created by Ikuo Takeuchi. This function does not compute anything useful, but is a heavily recursive program that illustrates the MIPS calling convention.

```

int tak (int x, int y, int z)

{

if (y < x)

return 1+ tak (tak (x - 1, y, z),

tak (y - 1, z, x),

tak (z - 1, x, y));

else

return z;

}

int main ()

{

tak(18, 12, 6);

}</pre>

```

The assembly code for this program is below. The tak function first saves its return address in its stack frame and its arguments in callee-saved registers, since the routine may make calls that need to use registers \$a0-\$a2 and \$ra. The function uses callee-saved registers since they hold values that persist over

the lifetime of the function, which includes several calls that could potentially modify registers.

```

.text

.globl

tak

tak:

$sp, $sp, 40

subu

$ra, 32($sp)

SW

SW

$s0, 16($sp)

move

$s0, $a0

$s1, 20($sp)

SW

$s1, $a1

move

$s2, 24($sp)

SW

$s2, $a2

move

$s3, 28($sp)

# temporary

```

The routine then begins execution by testing if y < x. If not, it branches to label 1, which is below.

```

bge $s1, $s0, L1 \# if (y < x)

```

If y < x, then it executes the body of the routine, which contains four recursive calls. The first call uses almost the same arguments as its parent:

```

addiu $a0, $s0, -1

move $a1, $s1

move $a2, $s2

jal tak # tak (x - 1, y, z)

move $s3, $v0

```

Note that the result from the first recursive call is saved in register \$53, so that it can be used later.

The function now prepares arguments for the second recursive call.

```

addiu $a0, $s1, -1

move $a1, $s2

move $a2, $s0

jal tak # tak (y - 1, z, x)

```

In the instructions below, the result from this recursive call is saved in register \$50. But, first we need to read, for the last time, the saved value of the first argument from this register.

```

addiu $a0, $s2, -1

move $a1, $s0

move $a2, $s1

move $s0, $v0

jal tak # tak (z - 1, x, y)

```

After the three inner recursive calls, we are ready for the final recursive call. After the call, the function's result is in \$ v 0 and control jumps to the function's epilogue.

This code at label L1 is the consequent of the *if-then-else* statement. It just moves the value of argument z into the return register and falls into the function epilogue.

```

L1: move $v0, $s2

```

The code below is the function epilogue, which restores the saved registers and returns the function's result to its caller.

The main routine calls the tak function with its initial arguments, then takes the computed result (7) and prints it using SPIM's system call for printing integers.

```

.globl main

main:

subu $sp, $sp, 24

sw $ra, 16($sp)

li $a0, 18

li $a1, 12

```

```

lί

$a2, 6

# tak(18, 12, 6)

jal

tak

$a0. $v0

move

$v0. 1

# print_int syscall

syscall

$ra, 16($sp)

1 W

addiu

$sp, $sp, 24

jr

$ra

```

# **A.7**

# **Exceptions and Interrupts**

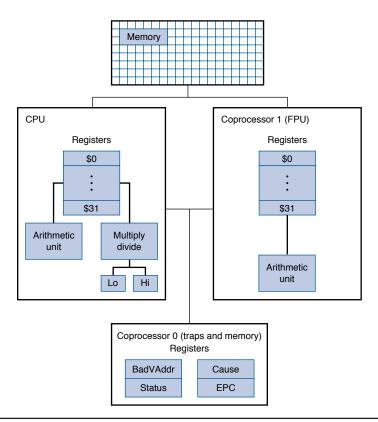

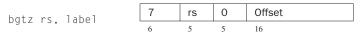

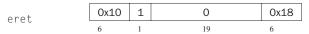

Section 5.6 of Chapter 5 describes the MIPS exception facility, which responds both to exceptions caused by errors during an instruction's execution and to external interrupts caused by I/O devices. This section describes exception and **interrupt handling** in more detail. In MIPS processors, a part of the CPU called *coprocessor 0* records the information that software needs to handle exceptions and interrupts. The MIPS simulator SPIM does not implement all of coprocessor 0's registers, since many are not useful in a simulator or are part of the memory system, which SPIM does not model. However, SPIM does provide the following coprocessor 0 registers:

**interrupt handler** A piece of code that is run as a result of an exception or an interrupt.

| Register<br>name | Register<br>number | Usage                                                              |

|------------------|--------------------|--------------------------------------------------------------------|

| BadVAddr         | 8                  | memory address at which an offending memory reference occurred     |

| Count            | 9                  | timer                                                              |

| Compare          | 11                 | value compared against timer that causes interrupt when they match |

| Status           | 12                 | interrupt mask and enable bits                                     |

| Cause            | 13                 | exception type and pending interrupt bits                          |

| EPC              | 14                 | address of instruction that caused exception                       |

| Config           | 16                 | configuration of machine                                           |

<sup>1.</sup> This section discusses exceptions in the MIPS32 architecture, which is what SPIM implements in Version 7.0 and later. Earlier versions of SPIM implemented the MIPS-I architecture, which handled exceptions slightly differently. Converting programs from these versions to run on MIPS32 should not be difficult, as the changes are limited to the Status and Cause register fields and the replacement of the <code>rfe</code> instruction by the <code>eret</code> instruction.

These seven registers are part of coprocessor 0's register set. They are accessed by the mfc0 and mtc0 instructions. After an exception, register EPC contains the address of the instruction that was executing when the exception occurred. If the exception was caused by an external interrupt, then the instruction will not have started executing. All other exceptions are caused by the execution of the instruction at EPC, except when the offending instruction is in the delay slot of a branch or jump. In that case, EPC points to the branch or jump instruction and the BD bit is set in the Cause register. When that bit is set, the exception handler must look at EPC + 4 for the offending instruction. However, in either case, an exception handler properly resumes the program by returning to the instruction at EPC.

If the instruction that caused the exception made a memory access, register BadVAddr contains the referenced memory location's address.

The Count register is a timer that increments at a fixed rate (by default, every 10 milliseconds) while SPIM is running. When the value in the Count register equals the value in the Compare register, a hardware interrupt at priority level 5 occurs.

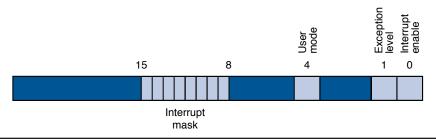

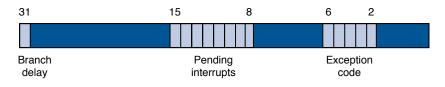

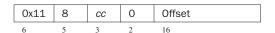

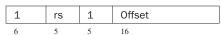

Figure A.7.1 shows the subset of the Status register fields implemented by the MIPS simulator SPIM. The interrupt mask field contains a bit for each of the six hardware and two software interrupt levels. A mask bit that is 1 allows interrupts at that level to interrupt the processor. A mask bit that is 0 disables interrupts at that level. When an interrupt arrives, it sets its interrupt pending bit in the Cause register, even if the mask bit is disabled. When an interrupt is pending, it will interrupt the processor when its mask bit is subsequently enabled.

The user mode bit is 0 if the processor is running in kernel mode and 1 if it is running in user mode. On SPIM, this bit is fixed at 1, since the SPIM processor does not implement kernel mode. The exception level bit is normally 0, but is set to 1 after an exception occurs. When this bit is 1, interrupts are disabled and the EPC is not updated if another exception occurs. This bit prevents an exception

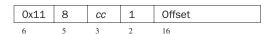

FIGURE A.7.1 The Status register.

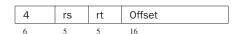

FIGURE A.7.2 The Cause register.

handler from being disturbed by an interrupt or exception, but it should be reset when the handler finishes. If the interrupt enable bit is 1, interrupts are allowed. If it is 0, they are disabled.

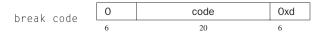

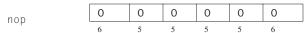

Figure A.7.2 shows the subset of Cause register fields that SPIM implements. The branch delay bit is 1 if the last exception occurred in an instruction executed in the delay slot of a branch. The interrupt pending bits become 1 when an interrupt is raised at a given hardware or software level. The exception code register describes the cause of an exception through the following codes:

| Number | Name | Cause of exception                                  |

|--------|------|-----------------------------------------------------|

| 0      | Int  | interrupt (hardware)                                |

| 4      | AdEL | address error exception (load or instruction fetch) |

| 5      | AdES | address error exception (store)                     |

| 6      | IBE  | bus error on instruction fetch                      |

| 7      | DBE  | bus error on data load or store                     |

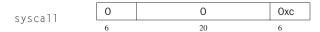

| 8      | Sys  | syscall exception                                   |

| 9      | Вр   | breakpoint exception                                |

| 10     | RI   | reserved instruction exception                      |

| 11     | CpU  | coprocessor unimplemented                           |

| 12     | Ov   | arithmetic overflow exception                       |

| 13     | Tr   | trap                                                |

| 15     | FPE  | floating point                                      |

Exceptions and interrupts cause a MIPS processor to jump to a piece of code, at address 80000180<sub>hex</sub> (in the kernel, not user address space), called an *exception handler*. This code examines the exception's cause and jumps to an appropriate point in the operating system. The operating system responds to an exception either by terminating the process that caused the exception or by performing some action. A process that causes an error, such as executing an unimplemented instruction, is killed by the operating system. On the other hand, other exceptions such as page faults are requests from a process to the operating system to perform a service, such as bringing in a page from disk. The operating system processes

these requests and resumes the process. The final type of exceptions are interrupts from external devices. These generally cause the operating system to move data to or from an I/O device and resume the interrupted process.

The code in the example below is a simple exception handler, which invokes a routine to print a message at each exception (but not interrupts). This code is similar to the exception handler (exceptions.s) used by the SPIM simulator.

#### **Exception Handler**

The exception handler first saves register \$at, which is used in pseudo-instructions in the handler code, then saves \$a0 and \$a1, which it later uses to pass arguments. The exception handler cannot store the old values from these registers on the stack, as would an ordinary routine, because the cause of the exception might have been a memory reference that used a bad value (such as 0) in the stack pointer. Instead, the exception handler stores these registers in an exception handler register (\$k1, since it can't access memory without using \$at) and two memory locations (save0 and save1). If the exception routine itself could be interrupted, two locations would not be enough since the second exception would overwrite values saved during the first exception. However, this simple exception handler finishes running before it enables interrupts, so the problem does not arise.

```

.ktext 0x80000180 mov $k1, $at  # Save $at register sw $a0, save0  # Handler is not re-entrant and can't use sw $a1, save1  # stack to save $a0, $a1  # Don't need to save $k0/$k1

```

# **EXAMPLE**

```

# Move Cause into $k0

mfc0

$k0, $13

srl

$a0, $k0, 2

# Extract ExcCode field

andi

$a0, $a0, 0xf

bgtz

$a0, done

# Branch if ExcCode is Int (0)

$a0, $k0

# Move Cause into $a0

mov

mfc0

$a1, $14

# Move EPC into $a1

print_excp

# Print exception error message

jal

```

Before returning, the exception handler clears the Cause register; resets the Status register to enable interrupts and clear the EXL bit, which allows subsequent exceptions to change the EPC register; and restores registers \$a0, \$a1, and \$at. It then executes the eret (exception return) instruction, which returns to the instruction pointed to by EPC. This exception handler returns to the instruction following the one that caused the exception, so as to not reexecute the faulting instruction and cause the same exception again.

```

mfc0

$k0, $14

# Bump EPC

done:

addiu

$k0, $k0, 4

# Do not reexecute

# faulting instruction

mtc0

$k0, $14

# EPC

mtc0

$0, $13

# Clear Cause register

$k0, $12

mfc0

# Fix Status register

# Clear EXL bit

andi

$k0, Oxfffd

ori

$k0, 0x1

# Enable interrupts

$k0, $12

mtc0

$a0, save0

٦w

# Restore registers

٦w

$a1, save1

mov

$at, $k1

# Return to EPC

eret

.kdata

save0: .word 0

savel: .word 0

```

**Elaboration:** On real MIPS processors, the return from an exception handler is more complex. The exception handler cannot always jump to the instruction following EPC. For example, if the instruction that caused the exception was in a branch instruction's delay slot (see Chapter 6), the next instruction to execute may not be the following instruction in memory.

# **A.8**

# **Input and Output**

SPIM simulates one I/O device: a memory-mapped console on which a program can read and write characters. When a program is running, SPIM connects its own terminal (or a separate console window in the X-window version XSpim or the Windows version PCSpim) to the processor. A MIPS program running on SPIM can read the characters that you type. In addition, if the MIPS program writes characters to the terminal, they appear on SPIM's terminal or console window. One exception to this rule is control-C: this character is not passed to the program, but instead causes SPIM to stop and return to command mode. When the program stops running (for example, because you typed control-C or because the program hit a breakpoint), the terminal is reconnected to SPIM so you can type SPIM commands.

To use memory-mapped I/O (see below), spim or xspim must be started with the -mapped\_io flag. PCSpim can enable memory-mapped I/O through a command line flag or the "Settings" dialog.

The terminal device consists of two independent units: a *receiver* and a *transmitter*. The receiver reads characters typed on the keyboard. The transmitter display characters on the console. The two units are completely independent. This means, for example, that characters typed at the keyboard are not automatically echoed on the display. Instead, a program echoes a character by reading it from the receiver and writing it to the transmitter.

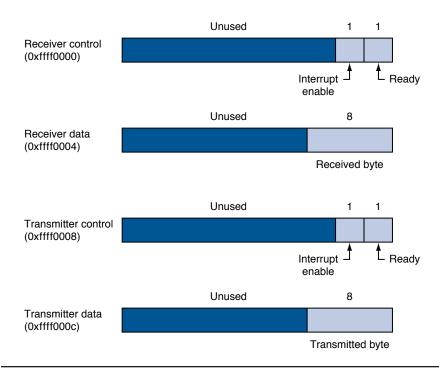

A program controls the terminal with four memory-mapped device registers, as shown in Figure A.8.1. "Memory-mapped" means that each register appears as a special memory location. The *Receiver Control register* is at location ffff0000<sub>hex</sub>. Only two of its bits are actually used. Bit 0 is called "ready": if it is 1, it means that a character has arrived from the keyboard but has not yet been read from the Receiver Data register. The ready bit is read-only: writes to it are ignored. The ready bit changes from 0 to 1 when a character is typed at the keyboard, and it changes from 1 to 0 when the character is read from the Receiver Data register.

A.8 Input and Output A-39

**FIGURE A.8.1** The terminal is controlled by four device registers, each of which appears as a memory location at the given address. Only a few bits of these registers are actually used. The others always read as 0s and are ignored on writes.

Bit 1 of the Receiver Control register is the keyboard "interrupt enable." This bit may be both read and written by a program. The interrupt enable is initially 0. If it is set to 1 by a program, the terminal requests an interrupt at hardware level 1 whenever a character is typed and the ready bit becomes 1. However, for the interrupt to affect the processor, interrupts must also be enabled in the Status register (see Section A.7). All other bits of the Receiver Control register are unused.

The second terminal device register is the *Receiver Data register* (at address ffff0004 $_{\rm hex}$ ). The low-order 8 bits of this register contain the last character typed at the keyboard. All other bits contain 0s. This register is read-only and changes only when a new character is typed at the keyboard. Reading the Receiver Data register resets the ready bit in the Receiver Control register to 0. The value in this register is undefined if the Receiver Control register is 0.

The third terminal device register is the *Transmitter Control register* (at address ffff0008<sub>hex</sub>). Only the low-order 2 bits of this register are used. They behave much like the corresponding bits of the Receiver Control register. Bit 0 is called "ready"

and is read-only. If this bit is 1, the transmitter is ready to accept a new character for output. If it is 0, the transmitter is still busy writing the previous character. Bit 1 is "interrupt enable" and is readable and writable. If this bit is set to 1, then the terminal requests an interrupt at hardware level 0 whenever the transmitter is ready for a new character and the ready bit becomes 1.

The final device register is the *Transmitter Data register* (at address ffff000 $c_{hex}$ ). When a value is written into this location, its low-order 8 bits (i.e., an ASCII character as in Figure 2.21 in Chapter 2) are sent to the console. When the Transmitter Data register is written, the ready bit in the Transmitter Control register is reset to 0. This bit stays 0 until enough time has elapsed to transmit the character to the terminal; then the ready bit becomes 1 again. The Transmitter Data register should only be written when the ready bit of the Transmitter Control register is 1. If the transmitter is not ready, writes to the Transmitter Data register are ignored (the write appears to succeed but the character is not output).